Intelligent Circuit Design and Implementation with ML in EDA

**Zhiyao Xie** Duke University

Advisors: Yiran Chen, Hai (Helen) Li

### **Chip Design Challenges**

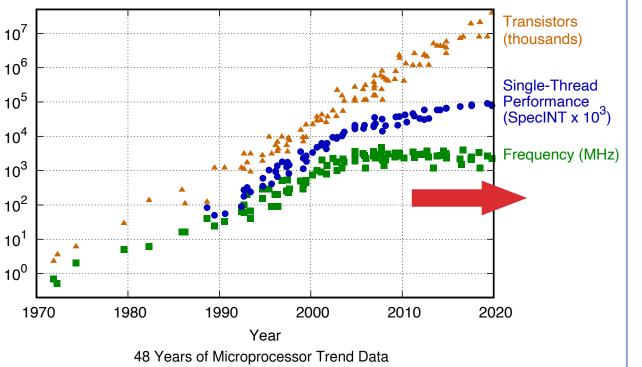

**Per-Core Performance Gain is Diminishing**

Diminishing performance gain and increasing design cost

Partially collected by M. Horowitz et al. Plotted by Karl Rupp, 2020

**IBS** Design Cost is Skyrocketing

**International Business Strategies, 2020**

### **My Related Works**

| PPA | Power       | Power & Power Delivery Challenges<br>[ICCAD'20], [ASPDAC'20],<br>[MICRO'21] (Best Paper Award)      |

|-----|-------------|-----------------------------------------------------------------------------------------------------|

|     | Performance | <b>Timing &amp; Interconnect Challenges</b><br>[ICCAD'20], [ASPDAC'21],<br>[TCAD'21] (under review) |

|     | Area        | Routability Challenges<br>[ICCAD'18], [DATE'18], [ICCAD'21]                                         |

|     |             | Overall Flow Tuning<br>[ASPDAC'20]                                                                  |

Covered in this talk

# **Routability Challenges**

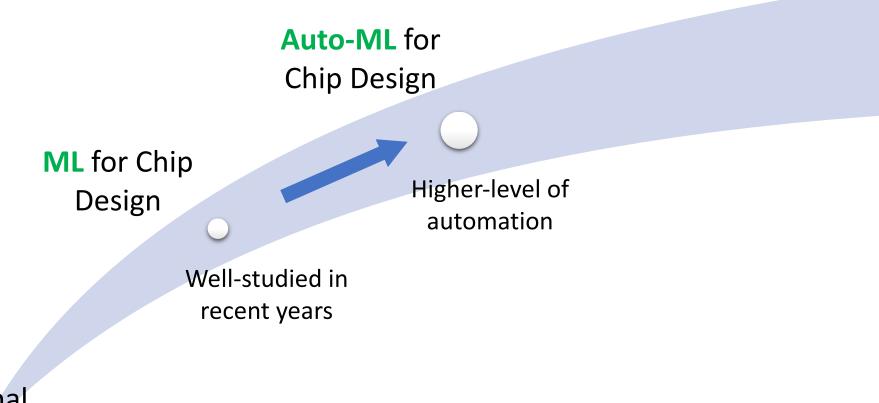

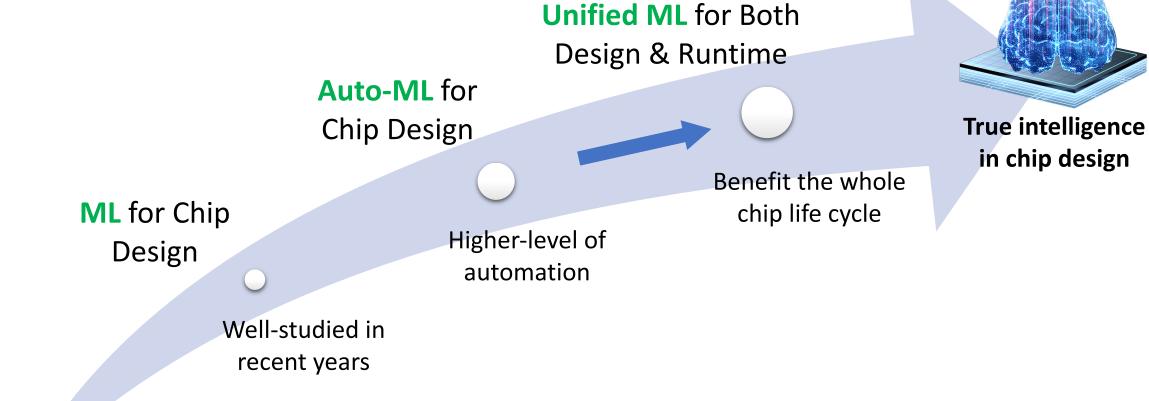

### My Roadmap Towards Intelligent Chip Design

True intelligence in chip design

ML for Chip Design

Well-studied in recent years

Traditional Chip Design

Source: Image adapted from Cadence Cerebrus.

# **First Deep Learning Method for Routability Prediction**

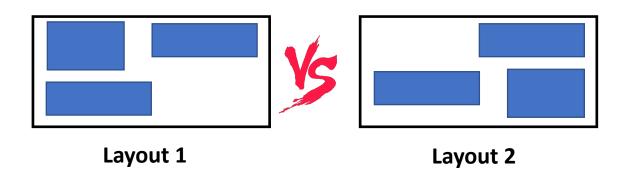

• Task 1: which one will result in less DRV count?

Customized CNN methods

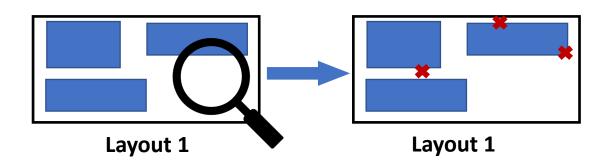

• Task 2: where are DRC violations?

Customized FCN methods

# **First Deep Learning Method for Routability Prediction**

• Task 1: which one will result in less DRV count?

Requires global routing: Hours \* Number of Layouts

In seconds, with close accuracy

• Task 2: where are DRC violations?

Requires detailed routing

More nours \* Iterations

In seconds, outperform previous works

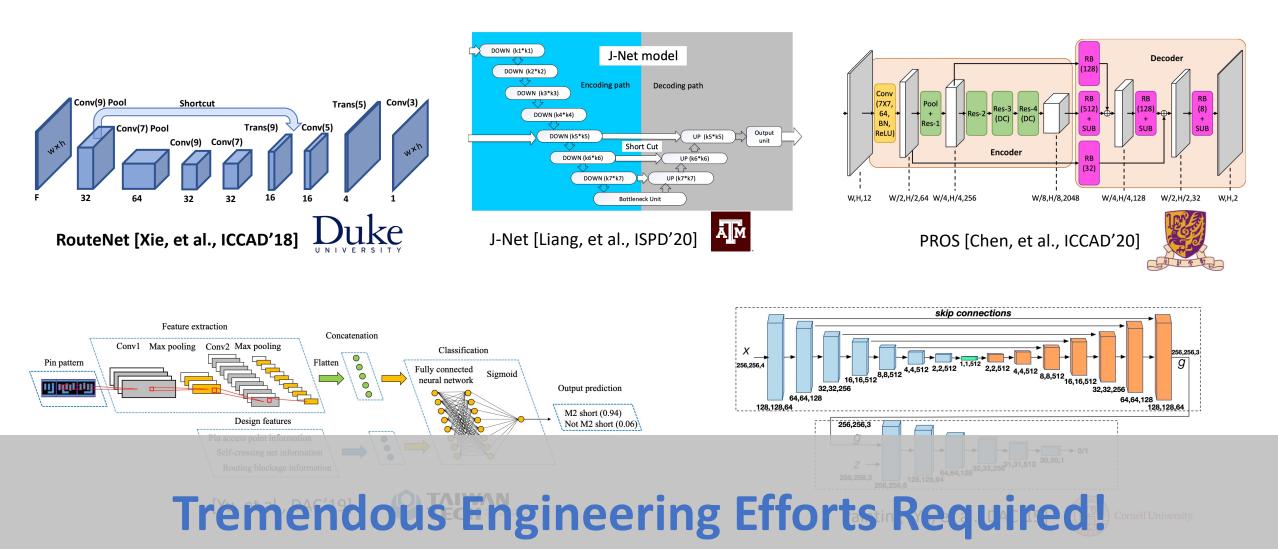

### **Many Excellent Deep Learning Methods**

### **My Roadmap Towards Intelligent Chip Design**

Traditional Chip Design

**True intelligence**

in chip design

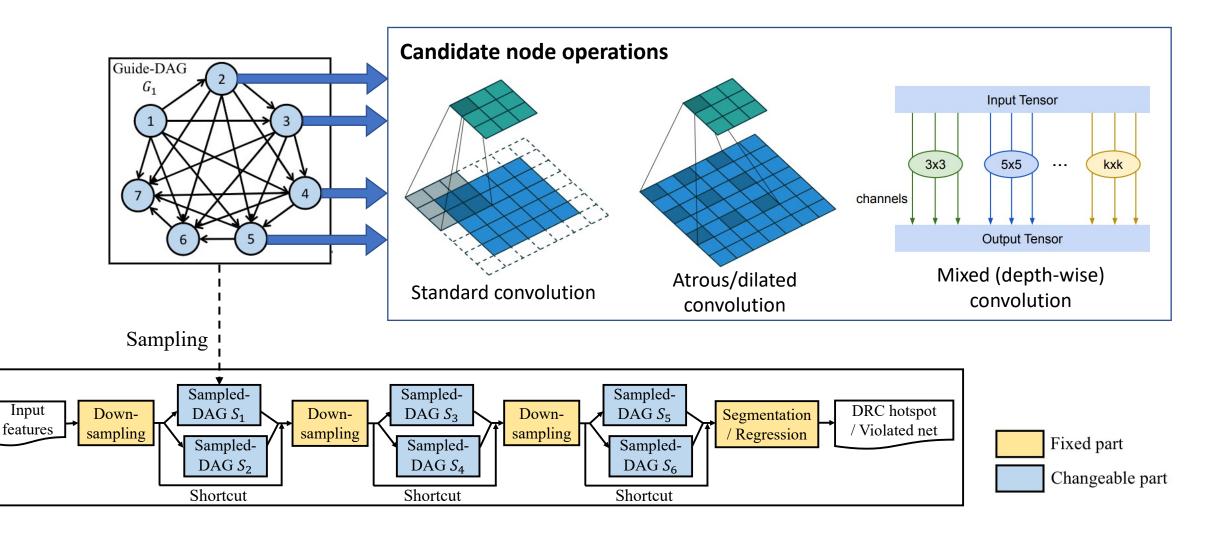

### **Automatic Estimator Development – Search Space**

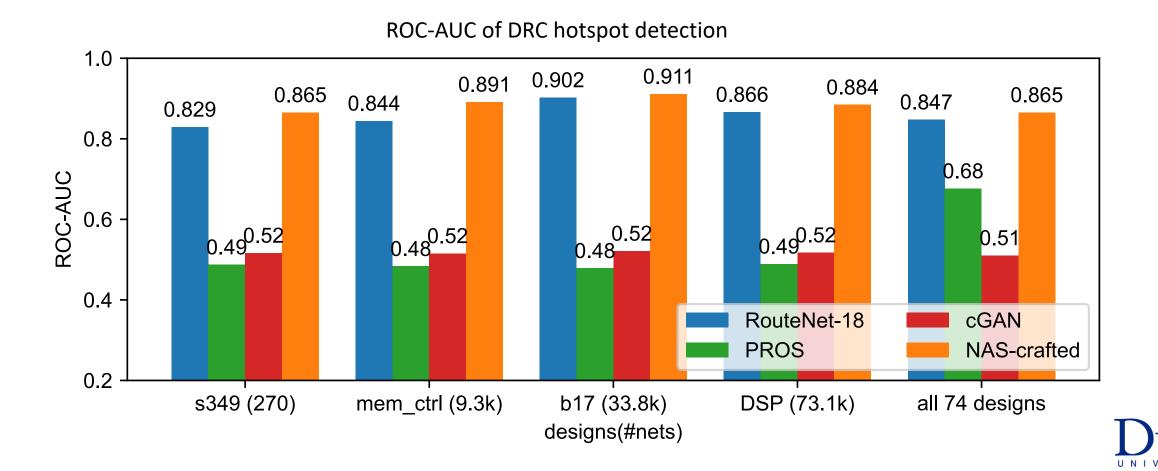

### **DRC Hotspot Detection Results**

- This model outperforms RouteNet [ICCAD'18], PROS [ICCAD'20], and cGAN [DAC'19]

- Developed without human in one day

**Case Study 2:**

# **Power & Power Delivery Challenges**

### **My Roadmap Towards Intelligent Chip Design**

Traditional Chip Design

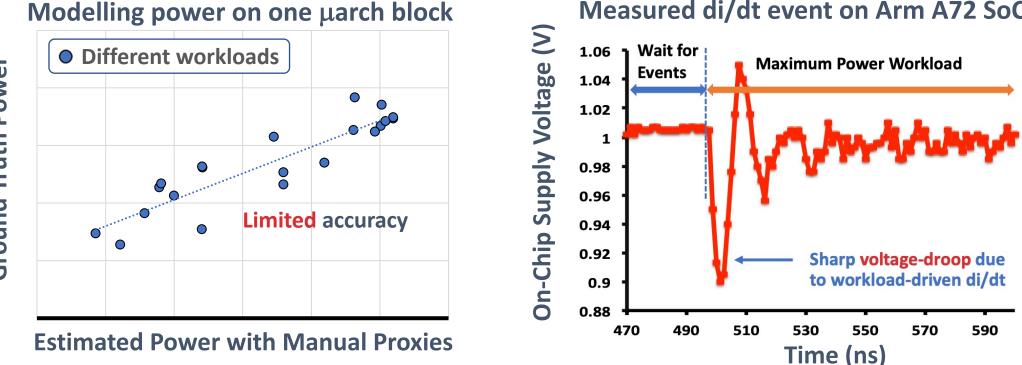

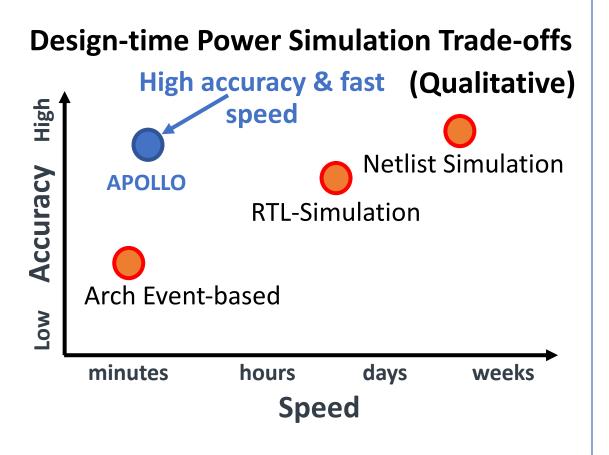

# **Challenge 1 – Design-time Power Introspection**

- Delivering generational performance gains adversely impacts CPU power

- Power-delivery resources **not keeping pace** with CPU power demands

- Increasing power-sensitivity drives the need for design-time introspection

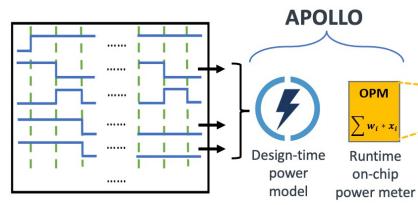

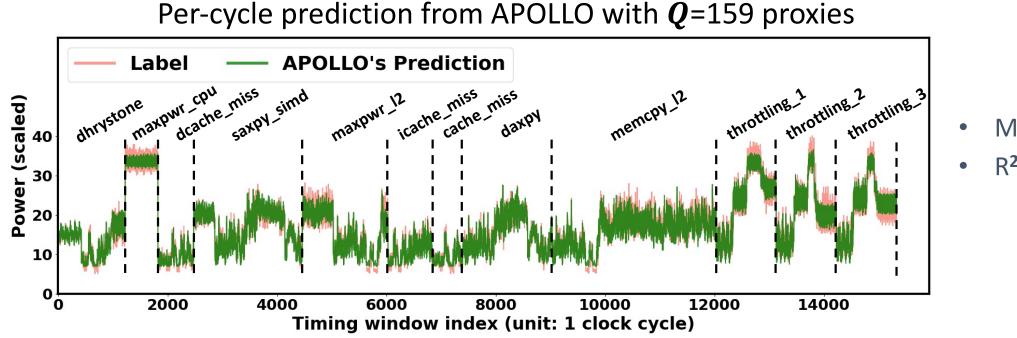

APOLLO [Xie, et al., MICRO'21] (Best Paper Award) Source: Arm Neoverse V1, 2021

# Challenge 2 – Run-time Power Introspection

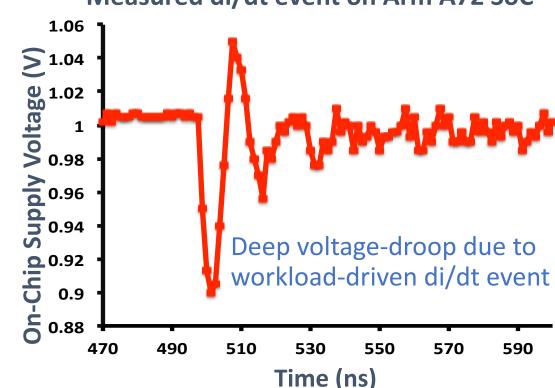

#### Measured di/dt event on Arm A72 SoC

- **Peak-Power mitigation** requires accurate power estimation to drive throttling ۲

- Manually inferring proxies is very difficult in complex modern CPUs

- Abrupt changes in CPU current-demand (di/dt event) leading to deep voltage-droop

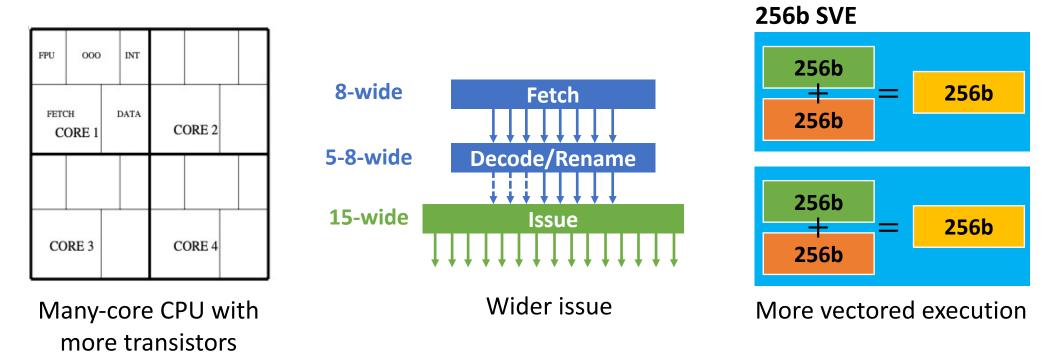

# **Power-Performance Trade-offs**

### **Generational gains in both IPC and FMAX**

• Wide issues queues, vector-execution

### Power consumption is adversely impacted

- Diminishing returns with scaling

- Increased transistor integration

### **Power-delivery resources not keeping pace**

- Resistive-interconnects in scaled nodes

- Package-technology unable to sustain di/dt demands

### Measured di/dt event on Arm A72 SoC

### Increasing power-sensitivity drives the need for power-introspection at design and runtime

# **Challenges from Both Design-time and Runtime**

A unified solution for both scenarios

### **APOLLO: A Unified Power Modeling Framework**

- Fast, yet accurate design-time simulation

- Low-cost, yet accurate runtime monitoring

- Design-agnostic automated development

**Neoverse N1 CPU floorplan**

### **Prediction Accuracy as Design-Time Power Model**

- MAE = 7.19%

- $R^2 = 0.953$

**Neoverse N1** (infra) Deployed in AWS Graviton

**Cortex A77** (mobile) Deployed In Snapdragon 865

# **Summary and Takeaway**

- Problem: Increasing Challenges in Chip Design

- Cost, time-to-market, reliance on designers, diminishing performance return, .....

- ML in chip design

- Less simulation time, faster feedback, less designer effort

- AutoML in chip design

- Reduces months of model development to hours, no developers

- Unified ML in both design & runtime

- Benefit the entire chip life cycle

# **Thanks! Questions?**

If you have further questions, please contact me: zhiyao.xie@duke.edu