# SCIENCE CHINA Information Sciences

POSITION PAPER

October 2024, Vol. 67, Iss. 10, 200402:1-200402:42 https://doi.org/10.1007/s11432-024-4155-7

Special Topic: AI Chips and Systems for Large Language Models

# Large circuit models: opportunities and challenges<sup> $\dagger$ </sup>

Lei CHEN<sup>5</sup>, Yiqi CHEN<sup>7</sup>, Zhufei CHU<sup>6</sup>, Wenji FANG<sup>3</sup>, Tsung-Yi HO<sup>1</sup>, Ru HUANG<sup>7,11</sup>, Yu HUANG<sup>4</sup>, Sadaf KHAN<sup>1</sup>, Min LI<sup>5</sup>, Xingquan LI<sup>9</sup>, Yu LI<sup>1</sup>, Yun LIANG<sup>7</sup>, Jinwei LIU<sup>1</sup>, Yi LIU<sup>1</sup>, Yibo LIN<sup>7</sup>, Guojie LUO<sup>8\*</sup>, Hongyang PAN<sup>2</sup>, Zhengyuan SHI<sup>1</sup>, Guangyu SUN<sup>7</sup>, Dimitrios TSARAS<sup>5</sup>, Runsheng WANG<sup>7</sup>, Zivi WANG<sup>1</sup>, Xinming WEI<sup>8</sup>, Zhiyao XIE<sup>3</sup>, Qiang XU<sup>1\*</sup>, Chenhao XUE<sup>7</sup>, Junchi YAN<sup>10</sup>, Jun YANG<sup>11</sup>, Bei YU<sup>1</sup>, Mingxuan YUAN<sup>5\*</sup>, Evangeline F.Y. YOUNG<sup>1</sup>, Xuan ZENG<sup>2</sup>, Haoyi ZHANG<sup>7</sup>, Zuodong ZHANG<sup>7</sup>, Yuxiang ZHAO<sup>7</sup>, Hui-Ling ZHEN<sup>5</sup>, Ziyang ZHENG<sup>1</sup>, Binwu ZHU<sup>1</sup>, Keren ZHU<sup>1</sup> & Sunan ZOU<sup>8</sup>

<sup>1</sup>Department of Computer Science and Engineering, The Chinese University of Hong Kong, Hong Kong 999077, China; <sup>2</sup>School of Microelectronics, State Key Laboratory of Integrated Chips and System, Fudan University, Shanghai 200433, China; <sup>3</sup>Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology,

Hong Kong 999077, China;

<sup>4</sup>Huawei HiSilicon, Shenzhen 518129, China;  $^5H\!uawei$  Noah's Ark Lab, Hong Kong 999077, China;

<sup>6</sup>Faculty of Electrical Engineering and Computer Science, Ningbo University, Ningbo 315211, China;

<sup>7</sup>School of Integrated Circuits, Peking University, Beijing 100871, China;

<sup>8</sup>School of Computer Science, Peking University, Beijing 100871, China;

<sup>9</sup>Peng Cheng Laboratory, Shenzhen 518052, China;

<sup>10</sup>School of Artificial Intelligence, Shanghai Jiao Tong University, Shanghai 200240, China;

<sup>11</sup>School of Integrated Circuits, Southeast University, Nanjing 210096, China

Received 22 April 2024/Revised 19 July 2024/Accepted 15 September 2024/Published online 25 September 2024

Abstract Within the electronic design automation (EDA) domain, artificial intelligence (AI)-driven solutions have emerged as formidable tools, yet they typically augment rather than redefine existing methodologies. These solutions often repurpose deep learning models from other domains, such as vision, text, and graph analytics, applying them to circuit design without tailoring to the unique complexities of electronic circuits. Such an "AI4EDA" approach falls short of achieving a holistic design synthesis and understanding, overlooking the intricate interplay of electrical, logical, and physical facets of circuit data. This study argues for a paradigm shift from AI4EDA towards AI-rooted EDA from the ground up, integrating AI at the core of the design process. Pivotal to this vision is the development of a multimodal circuit representation learning technique, poised to provide a comprehensive understanding by harmonizing and extracting insights from varied data sources, such as functional specifications, register-transfer level (RTL) designs, circuit netlists, and physical layouts. We champion the creation of large circuit models (LCMs) that are inherently multimodal, crafted to decode and express the rich semantics and structures of circuit data, thus fostering more resilient, efficient, and inventive design methodologies. Embracing this AI-rooted philosophy, we foresee a trajectory that transcends the current innovation plateau in EDA, igniting a profound "shift-left" in electronic design methodology. The envisioned advancements herald not just an evolution of existing EDA tools but a revolution, giving rise to novel instruments of design-tools that promise to radically enhance design productivity and inaugurate a new epoch where the optimization of circuit performance, power, and area (PPA) is achieved not incrementally, but through leaps that redefine the benchmarks of electronic systems' capabilities.

Keywords AI-rooted EDA, large circuit models (LCMs), multimodal circuit representation learning, circuit optimization

<sup>\*</sup> Corresponding author (email: gluo@pku.edu.cn, qxu@cse.cuhk.edu.hk, yuan.mingxuan@huawei.com) <sup>†</sup>The institutions and authors are ordered alphabetically.

## 1 Foundation model paradigm

The landscape of artificial intelligence (AI) has been profoundly transformed in recent years by the advent of large foundation models. These models, characterized by their vast scale and general applicability, have demonstrated an uncanny ability to understand, predict, and generate content with a level of sophistication that was previously the exclusive domain of human intelligence.

## 1.1 Rise of foundation models

Large foundation models represent a significant leap in AI. These models, typically pre-trained on webscale datasets using self-supervision techniques [1], have been adapted to excel in a wide array of downstream tasks. In the fields of natural language processing (NLP) and computer vision (CV), these models have not only set new benchmarks but have fundamentally redefined the realms of possibility.

In NLP, models like BERT [2] and its derivatives, including RoBERTa [3] and T5 [4], have revolutionized language understanding, especially in contextual interpretation of text, thereby enhancing complex language-based tasks. Concurrently, the decoder-only GPT series [5] has shown remarkable versatility, excelling in diverse tasks from creative writing to code generation and pointing towards the burgeoning potential of artificial general intelligence (AGI). In the CV area, self-supervised foundation models [6–8] have achieved competitive performances in image understanding tasks, rivaling fully supervised approaches.

The recent advent of multimodal foundation models has ushered in a new era of possibilities, integrating diverse data types such as text, images, and audio. A pioneering example is the CLIP model [9], which effectively bridges linguistic and visual data through contrastive learning. This innovation has set the stage for generative models like DALL-E [10] and Stable Diffusion [11], which demonstrate the capability to generate intricate images from textual descriptions, seamlessly blending visual and linguistic understanding. Additionally, the recently introduced promptable CV systems (e.g., SAM [12]) have exhibited exceptional zero-shot generalization in image segmentation, enabling precise object identification and extraction. The emergence of GPT-4V [13] and Gemini [14] further exemplifies the evolution of AI, seamlessly navigating and synthesizing multimodal information, thereby opening new avenues for innovation across various fields, from creative content generation to complex problem-solving in engineering and design.

Despite these advancements, the field of circuit design has only begun to scratch the surface of what foundation models can offer. This hesitant engagement contrasts starkly with the transformative potential these models hold for this important field.

#### 1.2 Unique challenge of circuit data

In the realm of circuit design, a notable phenomenon is the inherent similarity of many new designs to past iterations. Despite these similarities, designers frequently face the challenge of recreating or redesigning circuits from scratch, driven by the subtle yet critical nuances required to meet ambitious performance, power, and area (PPA) objectives. This repetitive process highlights the need for a learning solution that can effectively draw from historical successes and failures.

The emergence of AI for electronic design automation (AI4EDA) solutions [15] marks an attempt to integrate machine learning (ML) techniques into circuit design and optimization. Specifically, AI4EDA involves applying or adapting existing ML algorithms and AI methodologies to improve specific tasks within the current electronic design automation (EDA) framework. These advancements represent significant progress but often only augment, rather than redefine, existing methodologies. Typically, AI4EDA repurposes deep learning models from other domains for EDA tasks such as PPA estimation and optimization, verification, or fault detection. However, within the confines of traditional design frameworks, these models act more as individual analytical tools than as integral components of the design process, often failing to fully address the unique complexities of circuit data.

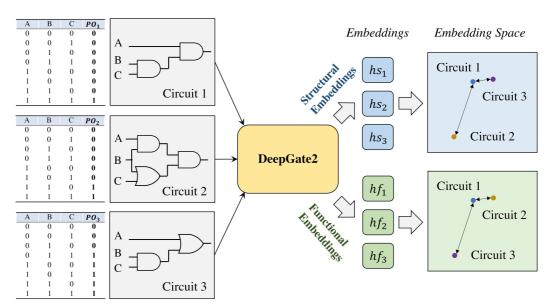

However, the distinctive nature of circuit data poses unique challenges for machine learning. Unlike text, images, or regular graph data, circuit design intricately intertwines computation with structure. Minor structural changes can lead to significant functional impacts, and vice versa. This interdependency renders the task of modeling circuits highly nuanced and complex. Without considering the above, existing AI4EDA solutions frequently fall short in achieving a comprehensive synthesis and understanding of the multifaceted interplay between electrical, logical, and physical aspects of circuit data, which is essential for truly innovative design synthesis.

Recent advancements in AI-rooted circuit representation learning, such as those presented in [16, 17], have begun to address these unique challenges. The integration of multimodal learning presents a significant opportunity to further enhance their effectiveness. By adopting the principles and capabilities demonstrated by existing foundation models on various types of data, we conceptualize a paradigm shift from AI4EDA to AI-rooted EDA from the ground up. Here, AI-rooted EDA refers to the development of new ML techniques and methodologies for EDA that are fundamentally based on AI principles from the ground up. It involves developing representation learning solutions for circuit data from scratch and creating new EDA solutions that inherently rely on AI techniques for their core functionality.

Pivotal to this vision is the development of sophisticated large circuit models (LCMs). Envisioned as models adept at integrating and interpreting diverse data types specific to circuit design, LCMs could potentially revolutionize the design, optimization, and verification processes of electronic circuits.

#### 1.3 Feasibility and promises of AI-rooted LCMs

In the world of semiconductor design, the potential for leveraging large circuit models is not just aspirational; it is rooted in a rich heritage of technological evolution.

Decades of research and development have yielded a vast repository of circuit data. Though proprietary barriers exist, there is enough in the public domain  $[18,19]^{1}$  to fuel the development of robust, intelligent models. The industry's long history provides data that is richly annotated with domain expertise, offering deep insights into the intricacies of circuit design.

Moreover, the landscape of circuit types, though vast, is marked by commonalities that transcend individual designs. Processors, domain accelerators (e.g., digital signal processors (DSPs) and AI accelerators), communication modules, and other core components display a pattern of design module reuse. Examples of these reusable modules include arithmetic units, various decoders, and cryptographic cores. This consistency provides a predictable pattern-akin to an inductive bias that is conducive to the application of machine learning models.

Advances in neural network architectures, particularly Transformers [20] and graph neural networks (GNNs) [21], are well-suited to capturing the complex, graph-like structure of circuit schematics. They present an opportunity to transform the intricate web of design elements into actionable insights, a feat previously unattainable. The AI advancements from other domains, e.g., CLIP model with multimodal machine learning capabilities [22] and large language models for code generation [23], further underscore the potential for transformative applications in LCMs. These capabilities could be adapted to address the unique challenges in circuit designs of various forms, enabling more nuanced and comprehensive modeling than ever before.

In summary, while the challenges are nontrivial, the development of LCMs is poised on a solid foundation of historical data, pattern prevalence, and cutting-edge computational techniques. The potential for LCMs to revolutionize the field of EDA is not just a theoretical possibility but a tangible goal, driven by the convergence of historical knowledge and modern AI advancements. By processing and interpreting a diverse array of data sources and formats, including schematic diagrams, textual specifications, register-transfer level (RTL) designs, circuit netlists, physical layouts, and performance metrics, LCMs can facilitate a 'shift-left' in the design methodology. This proactive AI-rooted approach enables the early identification of potential performance issues and design bottlenecks, streamlining the testing and redesign processes, and leading to more informed and efficient development cycles.

#### 1.4 Overview of this perspective paper

This paper embarks on a comprehensive exploration into the dawn of AI-rooted EDA, focusing on the development and application of large circuit models that inherently incorporate multimodal data. Spanning 9 sections, the sudy delves into the historical evolution of EDA, the current state of AI in this field, and the promising future shaped by LCMs.

Section 2 provides a historical overview of EDA, tracing its evolution alongside the semiconductor industry. It emphasizes how the field has navigated challenges of complexity through abstractions, setting a foundation for understanding the significance of LCMs in this evolving landscape. Next, we discuss the current integration of AI in EDA in Section 3, highlighting how deep learning has been utilized to improve EDA processes.

<sup>1)</sup> OpenCores. OpenCores. http://opencores.org/

In Section 4, we introduce AI-rooted LCMs, illustrating their departure from traditional AI4EDA approaches. It delves into how these models encapsulate the intricacies of circuit design, offering a more comprehensive approach to circuit analysis and even creation. Focusing on the development of unimodal circuit representation learning, Section 5 discusses its critical role in building the foundation for multimodal LCMs. It explores the nuances of this approach in achieving a thorough understanding of circuit data. Then, Section 6 navigates the transition to multimodal integration in LCMs. It discusses the development of techniques to align and integrate representations from different design stages, emphasizing the importance of preserving the original design intent.

Section 7 illustrates the potential applications of LCMs through case studies and envisioned scenarios, bridging the gap between theoretical concepts and practical implementations. In Section 8, we explore the application of LCMs in specialized circuit domains, discussing how these models can be adapted to cater to the unique needs of diverse circuit types other than standard digital circuits, including standard cell designs, datapath units, and analog circuits.

Next, we discuss the challenges and opportunities presented by the adoption of LCMs in EDA in Section 9. It highlights issues such as data scarcity and scalability, as well as the potential advancements these challenges can foster. Finally, the study concludes with a summary of the key insights and a forward-looking perspective in Section 10. It calls for continued collaboration between the AI and EDA communities and suggests future research avenues to further advance the field.

## 2 Historical odyssey of EDA

As we stand on the precipice of this new frontier of AI-rooted EDA, it is vital to appreciate the historical EDA journey. Understanding the evolution of cutting-edge EDA tools, methodologies, and philosophies will provide invaluable context for the challenges and opportunities that lie ahead.

#### 2.1 Core objectives and complexities in EDA

The odyssey of EDA is a chronicle of human ingenuity and technological advancement. It is a story that mirrors the exponential growth of the semiconductor industry, fueled by Moore's Law, and characterized by the ceaseless push for smaller, faster, and more efficient electronic devices. The journey from simple logic circuits to today's billion-transistor integrated circuits (ICs) has necessitated a layered hierarchical design methodology with the help of sophisticated EDA toolsets. This hierarchy, marked by stages such as specification, architecture design, high-level algorithm design, RTL design, logic synthesis, and physical design, allows for incremental refinement of the circuit design, each stage adding a layer of detail, ensuring functionality while striving for optimization.

The journey of EDA is not just marked by the sophistication of its tools but also by the fundamental goals that drive its evolution. Two core objectives have consistently shaped the development of EDA solutions:

• Equivalence and consistency across transformations. Ensuring that each transformation from behavioral descriptions to gate-level implementation and from logical to physical representation maintains the original design intent is essential. C-RTL equivalence checking, assertion-based verification (ABV), logic equivalence checking (LEC), sequential equivalence checking (SEC), and various types of simulation tools have been indispensable in this regard, providing designers with the assurance that despite the myriad of transformations a design undergoes, the end result is functionally equivalent to the original specifications. This integrity across various stages, including architecture design, logic synthesis, technology mapping, and place-and-route, is the bedrock upon which reliable electronic design is built.

• Optimization of PPA and other design factors. The relentless pursuit of optimizing performance, power, and area is central to EDA. As designs scale and complexities increase, the balance between these three aspects becomes more challenging to achieve. Tools dedicated to PPA optimization employ a variety of techniques, including predictive modeling, heuristic algorithms, and iterative refinement, to squeeze out efficiencies at every level of design. Meanwhile, the traditional PPA triad is no longer the sole focus. With the advent of ultra-deep submicron technologies, new concerns have emerged. Circuit reliability has taken center stage, with issues such as electromigration and thermal effects becoming critical. Manufacturability is another growing concern, as variability in fabrication processes can significantly impact yield and performance.

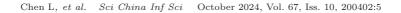

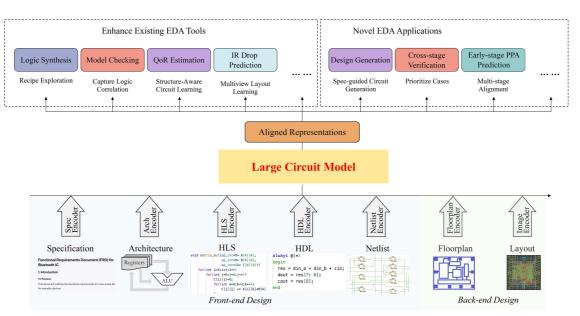

Figure 1 Typical (a) front-end and (b) back-end design flows.

In the fiercely competitive realm of electronic product development, reducing time-to-market (TTM) is paramount. The rapid evolution of consumer electronics, exemplified by the yearly refresh cycles of smartphones and wearables, underscores the urgency to expedite product launches to capture market share and meet consumer expectations. This pressure significantly impacts the EDA process, where the need for TTM can sometimes compromise design thoroughness, leading to potential flaws. For instance, under the gun to release the next generation of microprocessors, teams may bypass exhaustive verification in favor of meeting launch windows, risking the introduction of bugs into the final product. When such issues are not amendable through engineering change orders (ECO) [24], they necessitate a costly and time-consuming redesign, further exacerbating time-to-market pressures. Therefore, this cycle highlights the crucial need for EDA solutions that not only streamline design and verification processes but also ensure design accuracy from the outset.

#### 2.2 EDA for front-end design

In the 1980s, the growth of the semiconductor sector was hindered by the manual creation of large schematics, significantly limiting design productivity [25]. The narrative of front-end EDA tools is a testament to the field's evolution from the era of hand-drawn schematics to the sophistication of automated logic synthesis. This evolution has been underpinned by the introduction of hardware description languages (HDLs) like Verilog and VHDL, which have become the bedrock for digital design representation, simulation, and verification.

A typical front-end design flow, also known as logic design, is shown in Figure 1(a), in which the design specification is transformed into a logic netlist. The front-end design flow begins with a design specification, followed by architecture exploration. Subsequently, HDLs are created to translate the design into a form suitable for implementation, typically at the RTL abstraction level. The introduction of hardware construction languages (like Chisel [26]) and C/C++ high-level synthesis (HLS) adds a new dimension to front-end design and offers more flexibility and efficiency in addressing the complexities of modern front-end design.

After RTLs are created or generated from HLS tools, designers first use static analysis tools such as Lint [27] to identify potential errors and then apply various verification techniques, including logic simulation, emulation, and various formal methods (e.g., model checking). These techniques collectively contribute to validating the functionalities of the RTL design faithfully following the design specification. The verification and testing processes, spanning various transformations and stages, are integral components of design flows, typically consuming between 60% to 70% of the total engineering efforts allocated. This substantial investment underscores their critical role in ensuring the functionality and reliability of circuit designs. Across diverse abstracts of circuit designs, a plethora of verification techniques are employed, reflecting the nuanced requirements and challenges encountered at each stage of development. For example the C-RTL equivalence checking rigorously compares the RTL implementations against the C-based specification models. This verification method, as evidenced by studies such as [28, 29], is frequently applied, particularly in the context of data-path intensive designs, as highlighted by [30]. Given that circuit designs within this abstract primarily encapsulate hardware behavior while abstracting concrete physical details, theorem provers and satisfiability modulo theories (SMT) solvers emerge as pivotal tools for enhancing verification efficacy [31, 32].

Next, the RTL implementation undergoes the next stage in the design flow, wherein logic synthesis tools have revolutionized the way HDL code is transformed into gate-level representations. Logic synthesis typically involves three main steps: elaboration, logic optimization, and technology mapping. The primary objective of logic synthesis is to transform RTL codes into a gate-level netlist that meets specific design constraints while optimizing for power efficiency, maximizing performance, and minimizing the required silicon area, all within an acceptable timeframe. An indispensable aspect of logic synthesis involves conducting logic and sequential equivalence checks between optimized netlists and their initial counterparts, as underscored by studies such as [33–35]. Furthermore, custom equivalence checking techniques have been tailored to cater to specific circuit design requirements, such as those pertaining to clock-gating [36].

The collective progression of these front-end design and verification tools has not only streamlined the design process but also expanded the realm of what is possible in digital circuit design. As we navigate increasingly complex design landscapes, these tools have become indispensable in the relentless pursuit of innovation and optimization in digital systems.

#### 2.3 EDA for back-end design

For modern very-large-scale integration (VLSI) designs, the back-end design flow, also referred to as layout design, is depicted in Figure 1(b), transitioning from a gate-level or generic technology (GTech) netlist to a finalized layout [37].

This intricate process initiates with technology mapping, where a process library is applied to adapt the synthesized gate-level netlist to a specified technology library, with a keen focus on optimizing PPA constraints. To enhance testability for mass production, testability features such as scan chains, built-in self-test (BIST) circuits, and boundary scans are incorporated into the design. The subsequent phase, physical design, is tasked with establishing the chip's physical layout, entailing floorplanning, power delivery network (PDN) design, placement, clock tree synthesis (CTS), and routing. We list a few representative techniques for each task in the following.

• Floorplanning. Floorplanning establishes the chip's physical layout by optimizing the placement of major blocks to minimize interconnect lengths and ensure efficient silicon area utilization. It involves strategic arrangement considering timing, power, and thermal constraints to set a foundation for the design. Ref. [38] applied the simulated annealing optimization technique to VLSI floorplanning. The authors demonstrate how simulated annealing can effectively explore the solution space to find optimal or near-optimal floorplans, significantly influencing subsequent floorplanning methodologies. Ref. [39] introduced B\*-Trees for representing non-slicing floorplans. This representation allows for more flexible and efficient manipulation of floorplan topologies, leading to better optimization of area and wirelength in VLSI designs.

• PDN design. PDN design ensures a stable power supply across the chip, aiming to minimize voltage drop and maintain power integrity. The design of power and ground networks is crucial for delivering power efficiently, with considerations for IR drop, current density, and electromigration. Ref. [40] presented a methodology for designing power distribution systems in modern CMOS technology. It focuses on the selection and placement of decoupling capacitors to manage power integrity and reduce noise, offering practical guidelines and strategies for effective PDN design. Ref. [41] comprehensively discussed the principles and strategies for designing power distribution networks in VLSI circuits. It highlights the importance of hierarchical design, decoupling strategies, and the integration of power grids with signal routing to ensure robust and efficient power delivery.

• Placement. Placement optimizes the arrangement of standard cells or IP blocks within the floorplan to enhance performance, power, and area. It strategically positions components to reduce wire length, congestion, and considers timing and thermal impacts, employing algorithms to find an optimal configuration. Ref. [42] presented enhancements to the simulated annealing algorithm for row-based placement, incorporating techniques to improve convergence speed and solution quality. It significantly influenced the development of placement tools by demonstrating the effectiveness of simulated annealing in handling the placement problem. Ref. [43] formulated the placement problem as a quadratic programming task. It achieves high-quality placements with efficient computational performance by iteratively solving quadratic programs and slicing the problem into smaller sections. Ref. [44] introduced a fast and efficient analytical placement method that combines cell shifting, iterative local refinement, and a hybrid net model. This approach provides a balance between placement quality and runtime, making it suitable for large-scale designs. Ref. [45] was an analytical placer that addresses the challenges of large-scale mixed-size designs, including preplaced blocks and density constraints. By combining quadratic placement with discrete optimization, NTUPlace3 achieves excellent wire length and timing performance. A comprehensive survey can be found [46].

• **CTS.** CTS distributes the clock signal to synchronize the circuit's operations with minimal skew and jitter. Designing a balanced clock distribution network ensures reliable and synchronized performance across the chip. Ref. [47] introduced a zero-skew clock routing algorithm that aims to minimize wirelength while achieving zero skew. The approach uses a recursive geometric method to balance the clock tree, significantly reducing skew and improving timing reliability in VLSI designs. Ref. [48] resented an efficient buffer sizing algorithm aimed at reducing clock skew in the presence of process variations in VLSI designs. By quantitatively estimating the skew distribution through Monte-Carlo SPICE simulations and analyzing the impact of process variations on wire and buffer delays, the algorithm strategically adjusts the number and size of buffers on critical paths. A comprehensive survey can be found [37].

• Routing. Routing connects the components based on the established placement and netlist, aiming to complete interconnections without design rule violations or signal integrity issues. It optimizes for shortest paths, minimizes crosstalk and delay, and manages layer assignment and congestion. Ref. [49] introduced CUGR, a detailed-routability-driven 3D global routing algorithm that utilizes a probabilistic resource model to optimize routing quality and efficiency. The proposed approach incorporates two key techniques: 3D pattern routing, which combines pattern routing and layer assignment to optimize wire length and routability, and multi-level 3D maze routing, which uses a coarsened grid graph to efficiently find routable regions and detailed paths. Ref. [50] resented a negotiation-based global routing algorithm that focuses on achieving timing closure in complex VLSI designs. The algorithm iteratively adjusts routing paths and resources to meet timing constraints, ensuring reliable performance in the final design. Ref. [51] was a comprehensive tool for field-programmable gate array (FPGA) research that integrates packing, placement, and routing. The study demonstrates its effectiveness in optimizing FPGA designs, making it a widely used tool in the field. A comprehensive survey can be found for ASIC routing [52] and FPGA routing [53].

As chip designs escalate in complexity, the functionalities of back-end EDA tools extend beyond mere layout creation and routing, embracing a multi-faceted optimization challenge. For example, thermal analysis tools empower designers to forecast and address thermal hotspots, guaranteeing the chip's dependable performance across diverse environmental scenarios. Also, various design for yield (DfY) strategies are required to maximize the manufacturing yield by identifying and mitigating potential yield detractors, performing layout adjustments to address process variations, defect probabilities, and other manufacturing imperfections. Advanced DfY tools and methodologies analyze critical areas, apply lithography-friendly design principles, and optimize the layout to enhance robustness against variations in the fabrication process, ensuring higher yields and reliability of the final product [54].

Physical verification stands as a critical final step in the back-end design phase, ensuring that the chip layout adheres to all necessary specifications and standards before proceeding to manufacturing. This process involves an array of checks, including design rule checking (DRC), electrical rule checking (ERC), and layout versus schematic (LVS) verification. DRC is essential for validating the layout against a set of predefined rules to ensure manufacturability, focusing on physical dimensions and spacing between circuit elements to prevent fabrication errors. ERC goes a step further by examining the electrical integrity of the design, identifying issues such as signal integrity and power distribution problems, and ensuring the circuit meets its functional requirements. Lastly, LVS verification confirms that the layout accurately reflects the original schematic design, guaranteeing that the physical representation matches the intended circuit behavior. Together, these verification steps identify and rectify potential layout issues, safeguarding the correctness of the final chip.

In summary, the back-end EDA tools have fundamentally transformed the landscape of chip design, empowering designers to craft complex integrated circuits that house billions of transistors operating in unison on a single chip. As semiconductor technology progresses, the significance of EDA tools in the back-end design phase is poised to grow, continuing to fuel innovation and enhance efficiency in chip design research and engineering practices.

#### 2.4 EDA for specialized circuits

Beyond EDA tools for regular digital circuit designs, the field has witnessed a notable specialization in toolsets designed to meet the unique requirements of standard cells, datapath units, and analog circuits. This evolution underscores the maturation of EDA, providing designers with tailored solutions to optimize these fundamental components efficiently. Specialized EDA tools have become indispensable in addressing the nuanced challenges presented by each component type, enhancing the precision and performance of chip designs.

## 2.4.1 EDA for standard cells

Standard cells, the building blocks of digital ICs, follow predefined structures that align with a library's specifications, enabling their reuse across diverse designs. The focus of EDA tools in standard cell design is primarily on automating the layout generation process, encompassing crucial steps like placement and in-cell routing.

The placement process is dedicated to determining the optimal transistor locations within a cell to maximize space utilization while maintaining functionality and performance integrity. The common solution algorithms for the placement include dynamic program, reinforcement learning, and satisfiability modulo theories. Innovations in placement strategies, as highlighted in [55,56], have introduced methods to expedite this intricate procedure while ensuring routability and design efficiency. In contrast, in-cell routing tackles the intricate task of establishing connections within the cell, a process complicated by the rigorous area constraints of standard cells. The in-cell routing is usually solved by A-star, integer linear programming, and satisfiability modulo theories. This stage demands specialized routing solutions, distinct from those applied to broader digital circuits, to navigate the tight confines of cell layouts. Contributions from [57, 58] have provided targeted approaches to in-cell routing, addressing the unique challenges of standard cell design.

## 2.4.2 EDA for datapath circuits

The evolution of datapath circuits, from individual components such as adders, multipliers, and multiplyaccumulate (MAC) units to the entire datapath, is a testament to the continuous advancements in EDA technologies. Over the years, EDA tools have evolved to address the increasing complexity and performance demands of these critical components.

Adders. Adders serve as the cornerstone of arithmetic operations in digital circuits. The design of adders, from simple ripple-carry to more advanced carry-lookahead and prefix adders, has significantly benefited from EDA tools. These tools employ optimization algorithms to reduce latency, conserve area, and minimize power consumption, crucial for enhancing the overall performance of digital systems. The capability of EDA tools to simulate various adder configurations allows designers to select the most suitable architecture for specific applications, balancing speed with resource utilization.

Specifically, prefix-tree adders, recognized for their efficiency in parallel carry computation, have seen significant development and optimization through EDA solutions. Early adder designs, such as Sklansky, Kogge-Stone, and Brent-Kung adders [59], adopt predefined rules to generate adders with arbitrary bitwidths and optimized performance and area, laying a foundation for efficient design practices. Recent advancements have introduced more sophisticated designs such as the sparse Kogge-Stone and spanning tree adders, optimizing for both power efficiency and silicon area [60]. In addition to adder designs created by human experts, datapath compilers have become instrumental in navigating the vast prefix-tree design space and balance the trade-offs between different configurations, employing algorithmic [61] and heuristic methods [62, 63] to select the optimal structure for a given application scenario. The synthesized adders exhibit improved quality by effectively meeting various constraints such as delay, area, and fanout.

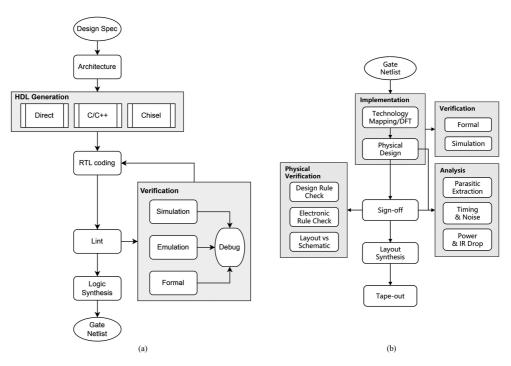

Figure 2 Typical datapath circuits design flow.

**Multipliers.** Multipliers are pivotal in performing fast arithmetic computations, crucial for applications ranging from general computing to specialized tasks in signal processing and machine learning. EDA technologies have facilitated the design of high-performance multipliers by exploring innovative architectures like Booth encoding and Wallace tree multiplication.

The Wallace tree technique involves grouping the partial products and compressing these groups in parallel, which is particularly favored in digital signal processing (DSP) and graphics processing units (GPUs) where rapid mathematical computations are critical. Similar to the development of prefix adders, early designs of Wallace trees relied on predefined rules to determine the grouping of partial products [64,65]. Recent advancements in efficient Wallace tree synthesis involve heuristic optimization algorithms, such as simulated annealing and integer linear programming [66], to assign compressors to different partial product groups, achieving reduced area and optimized delay. These advancements in automatic Wallace tree synthesis continuously enhance high-performance multiplier architectures to meet the evolving demands of semiconductor technology.

MAC units. The design of MAC units, essential for digital signal processing and deep learning applications, has similarly benefited from the innovations in EDA tools. By leveraging existing IP libraries [67] for design selection, or jointly utilizing automatic adder/multiplier synthesis tools, EDA tools could integrate optimized adder designs with efficient multipliers within MAC units to achieve high throughput and low latency.

Floating-point units (FPUs). Floating-point units are essential for executing arithmetic operations on floating-point numbers, a necessity in applications requiring a wide dynamic range, such as scientific computing, graphics, and machine learning algorithms.

The evolution of FPUs under the guidance of EDA tools highlights the industry's commitment to addressing the precision, performance, and power efficiency challenges inherent in floating-point operations. Techniques such as pipelining and parallel processing have been integral in enhancing the throughput of FPUs, allowing for simultaneous execution of multiple floating-point operations. Advances in EDA methodologies have facilitated the exploration of novel FPU designs, such as the adoption of fused multiply accumulate (FMA) units, as in MAC unit designs.

**Datapath circuits.** Beyond individual components, the design of entire datapath circuits, which comprise a combination of adders, multipliers, MAC units, and other logic elements, represents a complex challenge addressed by EDA tools.

These tools adopt a comprehensive strategy for refining datapath circuits, ensuring seamless integration and peak efficiency among components. As depicted in Figure 2, the design journey initiates with pinpointing a target application and its corresponding architectural design, thereby defining a broad and intricate design space. The application scope includes general computing [68] and specialized functions, such as high-performance computing [69], cryptography [70], and digital signal processing [71], targeting either traditional CPU designs or domain-specific accelerators. The design space diverges into two principal domains: the application space, outlining application-specific parameters like dataflow patterns or neural network mapping strategies [72], and the architecture space, detailing the structural and resource parameters, such as CPU pipeline width [73] or the quantity of MACs in a neural processing unit (NPU) [74].

The intersection of parameters from these domains establishes a "design point", which, upon postcompilation application mapping, is subjected to thorough evaluation and validation via cutting-edge

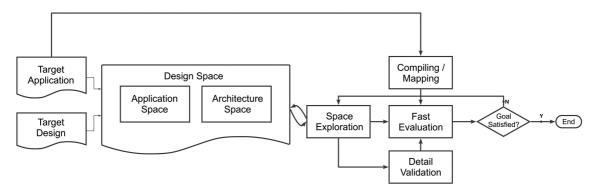

Figure 3 (Color online) Typical analog IC design flow.

EDA tools. This rigorous process of iteratively exploring and evaluating new design points to achieve the targeted objectives of power, performance, and area (PPA) is commonly referred to as design space exploration (DSE).

The progression to new design points is typically steered by optimization algorithms, which have advanced significantly. These optimizations fall into two categories, either by leveraging black-box optimization or incorporating domain knowledge. The black-box optimization formulates the DSE process as a general searching problem and proceeds without presuppositions about the design space, often utilizing simulated annealing (SA) [75], genetic algorithms (GA) [76], and Bayesian optimization (BO) [73,77]. Conversely, optimizations that incorporate domain knowledge demand an in-depth understanding of the architecture, aiming for enhancements through precise, targeted adjustments to the datapath. Techniques such as bottleneck analysis [78,79] often exhibit superior exploration efficiency by focusing on specific areas for improvement within the datapath architecture. Despite these advancements, traditional EDA methods for optimizing datapath design face significant challenges in integrating generic heuristic algorithms with highly customized domain-specific knowledge, which impedes the enhancement of design space exploration (DSE) efficiency.

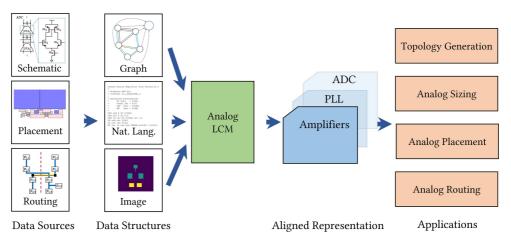

#### 2.4.3 EDA for analog circuits

The design process for analog and mixed-signal ICs significantly differs from digital design, showcasing the unique challenges and complexities of analog circuits.

Figure 3 illustrates a typical analog IC design flow, starting with a detailed set of circuit specifications covering area, power, and performance requirements. Analog EDA is typically divided into the front-end and the back-end. The front-end includes topology and device sizing, while the back-end focuses on the physical design. A survey for analog CAD can be found in [80].

The front-end design phase is crucial, establishing the pre-layout circuit netlist that defines the circuit's functionalities via meticulous topology design and device sizing. This phase sets the foundation for the circuit's operational features and optimization criteria. Analog device sizing recently is an active research field. Analog sizing decides the parameters for the devices, such as widths for transistors, in analog IC. A survey for the recent analog sizing research can be found in [81].

Moving to the back-end, attention turns to physical layout implementation. Analog physical design, including placement and routing stages similar to digital methods, requires a detailed approach due to analog circuits' sensitivity to parasitics. This phase also incorporates considerations for parasitic effects, component matching, and other layout-dependent factors essential for preserving the circuit's integrity and performance. A survey for analog layout automation can be found in [82].

A major challenge in analog design is performance optimization, marked by its nonlinearity and the lack of clear functional expressions. Despite these obstacles, the EDA community has significantly advanced the automation of analog IC design over the years. These efforts have covered various areas, such as topology selection or exploration [83], analog sizing [84], analog placement-and-route [85].

In summary, the journey of specialized circuit designs encapsulates a dynamic interplay of art and science. As technologies advance and design requirements become more stringent, the role of EDA tools in facilitating efficient, accurate, and innovative design solutions continues to be of paramount importance.

## **3** AI for EDA: state-of-the-art

The provess of deep learning, particularly its capability to discern patterns from historical design data, offers promising enhancements to EDA processes, as discussed in previous surveys [86–91]. This modern thrust is propelled by an ambition to harness the extensive repository of design knowledge accumulated across decades to drive superior and more efficient design methodologies.

#### 3.1 Supervised learning in EDA

The utilization of supervised learning in EDA represents a significant stride towards integrating AI into the optimization and estimation of design objectives. This subsection categorizes various supervised AI4EDA solutions based on their application stage within the standard design flow, highlighting seminal studies in each category for a focused overview. For those seeking an exhaustive review, references such as [15,92] offered comprehensive surveys on the subject.

#### 3.1.1 Pre-RTL ML methods

At the architecture level, supervised ML methods diverge into two primary categories: ML for rapid system modeling and ML as a design methodology.

• ML for fast system modeling. This approach employs ML to quickly estimate performance and power metrics of circuits and systems. Notable examples include the work by Joseph et al. [93] and Ithemal [94], which apply linear and recurrent neural network (RNN) models for CPU performance modeling, respectively. McPAT-Calib [95] enhances CPU power modeling by integrating ML models with the analytical tool McPAT for calibration. PANDA [96] advances this approach by reducing training data requirements and eliminating dependency on McPAT for power modeling. BOOM-Explorer [73] automates design space exploration for the RISC-V BOOM microarchitecture. Beyond CPUs, XAPP [97] predicts GPU performance by analyzing dynamic and static properties of single-thread CPU code, while Wu et al. [98] modeled GPU power by examining kernel scaling behaviors. SVR-NoC [99] focuses on predicting latency and waiting times in mesh-based network-on-chips (NoCs).

• ML as a design method. In microarchitecture design, ML techniques facilitate innovative solutions. Shi et al. [100] employed an LSTM model to derive insights from historical program counters for cache replacement using an SVM-based predictor. Pythia [101] reimagines prefetching as a reinforcement learning challenge, while Hermes [102] leverages ML to predict off-chip load request outcomes. Additional applications include task allocation [102], power management [103], and resource management for CPU [104] and AI accelerators [105].

In high-level synthesis, the application of ML models for rapidly estimating design metrics has become increasingly prevalent. For instance, Dai et al. [106] focused on timing and resource usage, Pyramid [107] estimates throughput, Ustun et al. [108] looked at operation delay, Zhao et al. [109] considered routing congestion, and Lin et al. [110] dedicated their efforts to power consumption analysis. These studies underscore the versatility of ML in covering a broad spectrum of design metrics, highlighting its capacity to provide comprehensive insights early in the design process.

Moreover, ML's role extends to facilitating design space exploration (DSE) in HLS, exemplified by the work of Ustun et al. [108], Liu et al. [111], and Meng et al. [112], who implement active learning strategies to navigate the DSE, using predictive ML models as stand-ins for actual synthesis processes. This approach allows for a more efficient evaluation of design alternatives without the need for exhaustive synthesis runs. Additionally, contributions by Kim et al. [113], Mahapatra et al. [114], and Wang et al. [115] demonstrate the integration of ML with traditional optimization algorithms, enhancing their efficacy in navigating complex design spaces. Sun et al. [116] introduced a novel approach using correlated multivariate Gaussian process models to capture the intricate interdependencies among multiple objectives across various design fidelities. Yu et al. [117] proposed the IT-DSE framework, leveraging a surrogate model pre-trained on historical design data to refine the search process, illustrating how accumulated design knowledge can be effectively reused to optimize new projects.

In the realm of tensor computations, HASCO [118] employs ML for DSE. This methodology optimizes both software programs and hardware accelerators, showcasing ML's capacity to bridge the gap between software and hardware domains to achieve optimized system performance.

#### 3.1.2 RTL-stage ML methods

At the RTL stage, innovative ML solutions have emerged to predict the PPA without conducting logic synthesis. Initial attempts, such as SNS by Xu et al. [119] and the work by Sengupta et al. [120], employ a methodology where the RTL code is converted into an abstract syntax tree (AST) format, from which features are extracted to forecast the design's PPA. Subsequent advancements, including SNS-v2 [121] and MasterRTL [122], claim enhanced accuracy compared to earlier efforts, showcasing the rapid progress in ML applications for RTL analysis. Additionally, there has been a focused effort on applying ML for precise timing or logic estimation [123, 124].

Power modeling at the RTL stage has also attracted lots of attention. There are two primary categories: design-time power estimation and runtime on-chip power modeling. For design-time estimation, PRIMAL [125] stands out for offering per-cycle power evaluations tailored to each target design, alongside other notable ML-based approaches [126, 127]. For runtime power modeling, DEEP [128] introduces an efficient on-chip model that incorporates low-overhead hardware design, utilizing ML to identify powercorrelated RTL signals, or 'power proxies'. This method, along with other ML-based on-chip power modeling solutions like [129, 130], demonstrates the potential of ML in creating dynamic power models that adapt to real-time conditions. Moreover, APOLLO [131] presents a versatile solution applicable to both design-time and runtime scenarios. Simmani [132] and the early power modeling work [133] focus on fast power emulation on FPGA and other platforms, highlighting the broader applicability of ML methods in facilitating efficient power analysis during the design phase.

In the realm of RTL testing and verification, Bayesian networks, as explored by Fine et al. [134], offer a probabilistic model-based approach for coverage-based test generation, underscoring the potential of ML in optimizing test planning. Design2Vec [135] advances this further by learning semantic abstractions of RTL designs, facilitating functionality prediction and efficient test generation that notably shortens verification cycles. Katz et al.'s [136] decision tree-based method for learning microarchitectural behaviors exemplifies ML's utility in enhancing test stimuli quality.

## 3.1.3 Netlist-stage ML methods

Within the netlist stage, supervised learning methods have been leveraged to address a spectrum of challenges including logic optimization [137], quality-of-results (QoR) prediction [138], and more [139,140].

• ML for logic optimization. ML-based models have shown significant effectiveness in evaluating synthesis quality and influencing the optimization process. For instance, LSOracle [141] utilizes ML to select the most suitable optimizers for different logic networks, thereby improving overall synthesis outcomes. Additionally, SLAP [142] targets design timing improvement by identifying and utilizing candidate cuts that enhance synthesis results during technology mapping. Their further work [143] demonstrates the ability of ML models to pinpoint post-routing timing critical paths, directing technology mapping efforts to minimize delays. Yu et al. [144] proposed classifying and selecting from multiple random synthesis flows based on their quality, focusing on the most effective ones. Their subsequent research [145] extends to predicting expected delay and area outcomes for synthesis flow candidates, providing a data-driven approach to guide synthesis decisions. Recent advancements, such as AlphaSyn [146], integrate Monte Carlo tree search with tailored learning strategies for area reduction, highlighting the potential of combining ML with heuristic search techniques for synthesis optimization. EasySO [147] proposes a hybrid discrete-continuous action space to jointly optimize the operation sequence and corresponding arguments.

• ML for QoR prediction. Following logic synthesis, innovative ML solutions can foresee the post-physical design quality of previously unknown circuit netlists. Tools like Net<sup>2</sup> [148] pave the way by predicting wirelength and timing information, effectively capturing the implications of placement on the netlist. PreRoutGNN [149] utilizes global circuit pre-training, local delay learning attentional cell modeling to realize pre-routing timing prediction. GRANNITE [150] advances this further by facilitating the propagation of the RTL toggle rate down to the gate-level netlist, aiming for rapid and accurate

average power estimation. Similarly, GRAPSE [151] evaluates average power based on unoptimized and unmapped netlists, showcasing improvements in both speed and precision of power estimation. Recently, DeepSeq [152] learns a generic sequential netlist representation that accurately embeds the switching activity behavior and predicts the dynamic power estimation.

Moreover, ML methods have shown exceptional prowess in deriving high-level abstractions from bitblasted netlists, unlocking new potentials across various domains within EDA. These high-level abstractions are instrumental in enhancing functional verification, logic minimization, datapath synthesis, and the detection of malicious logic within circuits. For instance, tools like ReIGNN [153] and GNN-RE [154] utilize ML for reverse engineering tasks, such as identifying state registers and deciphering the functionality of subcircuits. Additionally, ABGNN [155] leverages graph neural networks to delineate the boundaries of arithmetic blocks in flattened gate-level netlists, while Gamora [156] employs GNNs to infer high-level functional blocks from gate-level data. The success of these methodologies is largely attributed to the capacity of GNNs to discern intricate structural patterns and relationships within netlists, underscoring the transformative impact of ML in enhancing the efficiency and intelligence of EDA processes.

#### 3.1.4 Layout-stage ML methods

The layout stage presents a crucial phase where ML methods have been increasingly applied to predict or optimize various design metrics such as wirelength, routability, timing, and IR-drop [89, 157–160].

• ML for placement stage enhancements. The placement stage, which determines the optimal locations of macros and standard cells in the layout, is pivotal for achieving the desired design metrics. Early applications of ML aimed to augment traditional placement strategies. PADE [161] incorporates support vector machines (SVM) and neural networks for datapath extraction and evaluation, facilitating datapath-aware placement strategies. DREAMPlace, developed by Lin et al. [162], conceptualizes the placement challenge as akin to training a neural network, thus accelerating the global placement process by harnessing GPU computing capabilities. Building on DREAMPlace, Agnesina et al. [163] applied multi-objective Bayesian optimization for macro placement design space exploration, demonstrating the potential of ML in enhancing macro-placement outcomes.

ML also assists in predicting design metrics in the later routing phase, benefiting both iterative refinement and early-stage optimization. Many studies have explored early-stage routability prediction. RouteNet [164] uses a CNN to forecast the post-routing design rule violations (DRVs), thus avoiding difficult-to-route placements. Another study [165] guides macro placement based on predicted routability. Chang et al. [166] introduced a neural architecture search (NAS) for the autonomous development of routability prediction models, eliminating the need for manually designed machine learning models. Pan et al. [167] proposed a federated learning-based approach for routability evaluation, addressing data privacy concerns. To achieve better routability prediction performance, Zheng et al. [168] proposed a multimodal neural network Lay-Net, which aggregates both layout and netlist information. The ultimate purpose of routability prediction is to assist routability optimization. Liu et al. [169] incorporated a fully convolutional network (FCN)-based routability prediction model into the DREAMPlace framework, using it as a penalty factor to explicitly optimize for routability. PROS [170] introduces a routing congestion predictor as a plug-in for commercial placers, effectively adjusting cost parameters to mitigate congestion issues. Moreover, Zheng et al. [171] developed LACO, a look-ahead mechanism designed to address the distribution shift problem in congestion modeling.

Timing is another important metric for placement. The field of pre-routing timing prediction at the placement stage has witnessed a range of modeling approaches leveraging various features and machine learning techniques. Studies like those by Barboza et al. [172] and He et al. [173] have implemented tree-based methods, incorporating careful manual feature extraction. TF-Predictor [174] employs Transformers to treat timing paths as sequences, while Guo et al. [175] have devised a customized GNN inspired by static timing analysis mechanisms. Additionally, recent work by Wang et al. [176] addressed the restructuring of netlists due to timing optimization, integrating graph data from netlists with layout image information through multimodal fusion. Moreover, Liang et al. [177] focused on cross-talk prediction, exploring various machine learning models for this purpose. To reduce turn-around time at the prerouting stage, Liu et al. [178] proposed a concurrent learning-assisted early-stage timing optimization framework called TSteiner, which guides the refinement of Steiner points based on gradients obtained from a GNN-driven timing evaluator.

• ML for sign-off enhancements. During the routing and sign-off stages, the precision of sign-off

timing, especially using the path-based static timing analysis (PBA), becomes crucial. However, the PBA process is time-consuming, leading to the application of machine learning models for predicting path-based timing based on quicker graph-based analysis (GBA) results. The pioneering work by Kahng et al. [179] was instrumental in predicting PBA from GBA using carefully engineered features and a tree-based model. Subsequent studies, such as [174, 180], have delved into various machine learning models, including transformers and GNN, to enhance the accuracy of GBA-PBA predictions.

Additionally, IR-drop analysis is a critical component in the sign-off stage. Several studies have investigated rapid IR-drop estimation using machine learning, focusing on either static or dynamic analysis to cater to different requirements. For instance, studies like IncPIRD [181] and XGBIR [182] concentrate on static IR-drop analysis. In contrast, studies such as [183] target dynamic IR-drop analysis.

• ML for manufacturability enhancements. In the field of design for manufacturing (DFM), leveraging ML has become pivotal for bolstering the reliability of lithography and manufacturing processes, with layout patterns often analyzed as images. Studies like GAN-SRAF [184], GAN-OPC [185], DevelSet [186], and L2O-ILT [187] use various ML methods to improve mask synthesis printability. Other studies, such as those by Watanabe et al. [188], Ye et al. [189], Lin et al. [190], and Chen et al. [191], focus on lithography modeling to simulate printed patterns from mask clips. For identifying layout patterns prone to printing failures like shorts or opens, ML-enhanced lithography hotspot detection is explored in various studies. For example, Yang et al. [192] proposed to extract layout features with discrete cosine transform and utilized a CNN architecture for hotspot detection. The performance is further improved with the proposed bias learning algorithm because of the imbalanced dataset. Inspired by the object detection problem in computer vision, Chen et al. [193] proposed to detect multiple hotspots within large layouts simultaneously. In [194], the binarized neural network is utilized to speed up the hotspot detection flow. New network architecture is designed based on residual networks to achieve higher detection accuracy and performance. Additionally, ML further contributes to yield estimation and analysis, as seen in studies like Ciccazzo et al. [195], Nakata et al. [196], and Alawieh et al. [197].

#### 3.1.5 Cross-stage ML methods

In addition to stage-specific applications, ML4EDA has significantly impacted the broader task of design flow tuning, garnering substantial interest.

Kwon et al. [198] introduced a novel approach that blends tensor decomposition with regression analysis to recommend parameters for both logic synthesis and physical design stages, demonstrating ML's capability to streamline design parameterization. FIST [199] utilizes a clustering strategy to automate the adjustment of flow parameters, aiming for enhanced design quality. Furthermore, PTPT [200] presents a multi-objective Bayesian optimization framework equipped with a multi-task Gaussian model, significantly improving the design flow tuning process's efficiency.

Verification, a critical component throughout the design process, has also seen the integration of ML to validate circuit design correctness. Cho et al. [201] proposed an efficient lithography-aware router, which moves lithography verification to the routing stage, effectively enhancing the quality of the printed layout.

#### 3.2 Reinforcement learning in EDA

Reinforcement learning (RL) in EDA has emerged as a powerful method for navigating the expansive solution spaces inherent in logic synthesis and physical design, often uncovering innovative solutions that surpass traditional, intuition-based approaches. Innovations like Synopsys.ai [202] underscore this trend, showcasing AI-driven methodologies that enhance PPA metrics across the design spectrum.

In logic synthesis, Liu et al.'s PIMap framework [203] exemplifies the application of RL by optimizing LUT-based FPGAs through graph partitioning and iterative synthesis operation selection, leveraging parallelization for efficiency gains. FlowTune, introduced by Yu [204], employs a multi-stage multi-armed bandit (MAB) strategy to constrain the search space and streamline the synthesis process. Pei et al.'s AlphaSyn [146], utilizing a domain-specific Monte Carlo tree search (MCTS), and Zhu et al.'s approach [205], framing logic synthesis as a Markov decision process (MDP) with a graph convolutional network (GCN), both illustrate the capacity of RL to thoroughly explore synthesis strategies. DRiLLS by Hosny et al. [206] and subsequent studies like those by Peruvemba et al. [207] further extend this exploration, introducing constraints and optimization targets into the RL models to fine-tune synthesis outcomes. RL has also been applied to logic optimization challenges. For instance, Haaswijk et al. [208]

and Timoneda et al. [209] leveraged policy gradient methods and GCNs to optimize majority-inverter graphs (MIGs), showcasing RL's adaptability to various logic structures.

In physical design, the application of RL ranges from automating chip floorplanning, as demonstrated by Mirhoseini et al. [210], to minimizing area and wirelength in floorplanning processes like GoodFloorplan [211]. At the stage of placement and routing, DeepPlace [212] and PRNet [213] incorporate RL to bridge the placement with the subsequent routing task and HubRouter [214] devises a framework that integrates a deep generative model with RL to expedite the resolution of routing problems. Agnesina et al.'s [215] used of RL to tune physical design flows for improved PPA metrics and RL-Sizer by Lu et al. [216] for gate sizing highlight RL's potential to refine physical design processes, including timing optimization [217] and mask optimization in the RL-OPC process [218]. For clock tree synthesis, research efforts are directed toward predicting the quality of the clock network and enhancing timing optimization by leveraging clock skew. GAN-CTS [219] employs a conditional generative adversarial network (GAN) combined with reinforcement learning for predicting and optimizing CTS outcomes.

#### 3.3 Leveraging large language models in EDA

The integration of generative AI, particularly large language models (LLMs), into IC designs is emerging as a transformative trend. By utilizing proprietary datasets, IC design companies can develop AI assistants to enhance and expedite the design process. These tools, capable of providing in-depth insights, automate and refine traditionally manual tasks like design conceptualization and verification. Consequently, a growing body of research explores the application of LLMs in EDA, tackling a broad spectrum of tasks including RTL code generation, task planning, script generation, and bug fixing. While still in the early stages, these studies underscore the profound potential of LLMs to improve the efficiency and efficacy of EDA tools.

This section delves into the use of LLMs for RTL code generation, a key area of focus. It categorizes the research into LLM-aided RTL design generation and verification. Additionally, we explore LLM applications in generating EDA scripts and high-level architecture design.

## 3.3.1 RTL generation through LLMs

The advent of large language models has ushered in a new era for RTL code generation, offering solutions that have the potential to redefine traditional approaches.

Early explorations in this domain primarily focused on evaluating models against simple design tasks, hindered by the absence of standardized benchmarks. This challenge has been recently addressed with the introduction of comprehensive benchmarks like RTLLM [220] and VerilogEval [221], facilitating a more robust comparison of LLM capabilities across complex design tasks. RTLLM stands out by providing an open-source benchmark with thirty detailed design tasks, accompanied by ground-truth RTL code for functionality verification. It emphasizes three core objectives: syntax correctness, functional accuracy, and design quality, showcasing a significant leap in performance through innovative prompt engineering techniques like self-planning. Similarly, VerilogEval expands the evaluation framework by gathering Verilog code from diverse sources to construct over 100 test cases. Its approach of collecting additional RTL code for model training demonstrates comparable performance with advanced models like GPT-3.5, yet its training data and model remain unreleased to the public.

Commercial LLMs are utilized for RTL generation, with initial attempts applying GPT-2 for code completion showing promising results [222]. Subsequent developments have introduced tools like ChipGPT [223] and AutoChip [224], which leverage GPT-3.5 to refine code generation through prompt engineering and feedback loops, further reducing the need for human intervention. Chip-Chat's [225] achievement in designing a microprocessor with GPT-4 underscores LLMs' potential to autonomously generate hardware description languages.

Recently, the shift towards fine-tuning open-source LLMs presents a viable alternative for customized model development, addressing privacy concerns in VLSI design. Projects like ChipNeMo [226], RTL-Coder [227], and BetterV [228] have demonstrated significant advancements, employing domain adaptation techniques and automated training dataset generation to enhance LLM efficiency and performance for RTL code generation.

#### 3.3.2 Enhancing verification with LLMs

The application of LLMs extends beyond RTL code generation to the verification processes. These models assist in both functional correctness and security analysis, showcasing their versatility and depth in enhancing design validation.

Functional verification through LLMs. LLMs have made significant strides in functional verification by translating natural language specifications into SystemVerilog assertions (SVAs). This process ensures that RTL implementations adhere to their intended specifications. Notably, Refs. [229, 230] leveraged human-written specification sentences alongside RTL designs to generate precise SVAs. AssertLLM [231] takes a proactive approach by generating assertions directly from comprehensive specification documents, even before the RTL design phase. This method is complemented by a benchmark set that pairs natural language specifications with golden RTL implementations, offering a robust framework for evaluating assertion generation. Furthermore, LLMs have achieved success in solving the Boolean satisfiability (SAT) problem [232], which can be applied to verify arithmetic circuits.

Security verification leveraging LLMs. Security validation, critical in identifying and mitigating common vulnerability enumerations (CWEs), has also benefited from LLM integration. Ahmad et al. [233] demonstrated the capacity of LLMs to repair hardware security bugs, provided the bug's location is known. Further research includes leveraging ChatGPT to recommend secure RTL code [234] and employing LLMs in hardware security assertion generation [235]. The latter develops an evaluation framework and benchmark suite that encompasses real-world hardware designs, illustrating LLMs' potential to contribute significantly to security validation efforts.

#### 3.3.3 EDA script generation and architecture design

The versatility of LLM-based solutions in EDA also extends to embrace tasks like EDA script generation and high-level architectural design.

**EDA script generation.** ChatEDA [236] introduces an LLM-based agent designed to facilitate EDA tool control using natural language, offering an alternative to traditional TCL scripts. This agent supports a range of operations from RTL code to the graphic data system version II (GDSII), encompassing automated task planning, script generation, and task execution, making EDA tools more accessible and efficient.

Architectural design. GPT4AIGChip [237] leverages LLMs to generate C code for AI accelerator high-level synthesis. Similarly, Yan et al. [238] examined the use of LLMs in optimizing compute-inmemory (CiM) DNN accelerators, showcasing the model's potential in enhancing computational efficiency. Further extending the scope, Liang et al. [239] delved into quantum architecture design, exploring the frontiers of quantum computing. SpecLLM [240] contributes to this growing body of work by providing a dataset of architecture specifications at various abstraction levels, investigating LLMs' capabilities in both generating and reviewing these specifications.

## 3.4 AI for specialized circuits

The advent of AI4EDA also presents a unique opportunity to redefine the design and optimization of specialized circuits, including standard cells, datapath components, and analog circuits.

#### 3.4.1 AI for standard cells

The application of AI in standard cell design, particularly in placement and routing, presents a unique set of challenges due to their high density and strict routability requirements. An AI-assisted approach, utilizing reinforcement learning, has been shown to improve placement sequences and routability, offering better wire length performance [241]. Additionally, RL methods have been used to address DRC violations post-routing [242], simplifying the routing process and enabling the use of A-star or maze routing for optimal solutions. Machine learning techniques have also facilitated the adaptation of DRC rules, easing the migration of standard cell layouts across technology nodes [243]. A notable area for AI application is in the evaluation of standard cell layouts, where machine learning models can rapidly assess performance without the need for detailed simulations.

#### 3.4.2 AI for datapath circuits

Machine learning-based methods are emerging as a powerful tool for optimizing the design of datapath circuits, enabling enhanced efficiency and performance. By leveraging the distinct functionalities and structures of datapath circuits, AI can facilitate a more effective design optimization process.

Roy et al. [244] employed machine learning to predict the Pareto frontier for adders within the physical design domain. It exemplifies how machine learning can be leveraged for design space exploration, providing insights into optimal design configurations. Utilizing an integrated framework that combines variational graph autoencoders with graph neural processes, Ref. [245] developed a novel approach for automatic feature learning of prefix adder structures. This method facilitates sequential optimization, enabling the exploration of Pareto-optimal structures alongside quality metrics. Another study [246] employs multi-perception neural networks to analyze and learn from existing designs and performance data of adders and multipliers. This approach not only achieves high prediction accuracy but also outpaces traditional optimization methods in speed. Moreover, the RL-MUL framework [247] introduces a novel RL strategy for enhancing multiplier designs. By adopting matrix and tensor representations for the compressor tree and leveraging CNN as the agent, this method allows for dynamic adjustments to the multiplier structure, showcasing the adaptability of AI in complex design optimization.

#### 3.4.3 AI for analog circuits

AI's integration into analog IC design automation marks a pivotal advancement, enhancing both the efficiency and effectiveness of algorithms. This integration capitalizes on graph and image data representations, mirroring circuit topologies and layouts [248], to address the challenges inherent to analog design-namely, slow performance evaluation, and high search complexity.

AI for analog topology generation. The integration of AI into the generation of analog topologies is revolutionizing the field by speeding up evaluation processes, honing in on more efficient search spaces, and improving optimization techniques. Among the diverse approaches, variational graph autoencoders (VGAEs) have been employed for circuit topologies as showcased by Lu et al. [249], while RL-based methods have been applied to power converters, as demonstrated by Fan et al. [250]. More broadly, Zhao et al. [251] have utilized RL alongside predefined libraries to address a wider array of problems. Poddar et al. [252] have introduced a data-driven strategy for selecting topologies and sizing devices, employing a variational autoencoder (VAE) to synthesize data and thereby reduce simulation expenses. To tackle the complexities of large circuit design, hierarchical methods are being investigated. Lu et al. [253] have put forward a bi-level Bayesian optimization technique for  $\Delta$ - $\Sigma$  modulators, while Fayazi et al. [254] and Hakhamaneshi et al. [255] have delved into intermediate topology representations and GNN models for voltage node prediction, respectively. These developments suggest that AI holds significant promise in streamlining the generation of complex topologies, including those of larger circuits comprising multiple sub-circuits.

**AI** for analog sizing. AI is playing a pivotal role in advancing optimization within the realm of analog sizing, notably through the use of ML as surrogate models and RL for direct optimization efforts. ML models, particularly feed-forward neural networks, have been adeptly trained to closely approximate circuit performance metrics. These models, when operated in inference mode, enable the prediction of new, unseen design points, thereby enhancing the efficiency of the search process [256]. On another front, RL, especially via the GCL-RL algorithm, marries RL techniques with graph neural networks to adeptly optimize analog sizing across varying technological domains. This synergy leverages GNNs' robust capability to encapsulate circuit topologies within the optimization framework [257]. Such methodologies, along with other RL-centric approaches, aim squarely at the intricate balance between global exploration and local exploitation, a balance that is essential for achieving sample efficiency in analog sizing tasks. Innovative strategies, including the use of Voronoi trees for the decomposition of the design space and Monte Carlo tree search (MCTS) for honing in on local search areas, highlight the complex tactics employed to navigate the vast, high-dimensional optimization landscapes with greater efficiency [258]. The field's progress and the diverse methodologies employed are thoroughly reviewed in a dedicated book chapter, offering a deep dive into the significant advancements and techniques in ML applications for analog sizing [81].

AI for analog layout automation. The application of AI in analog layout automation significantly enhances processes such as constraint extraction, placement, and routing, as extensively reviewed in [259].

For constraint extraction in analog layouts, graph-based methodologies are pivotal for identifying

Chen L, et al. Sci China Inf Sci October 2024, Vol. 67, Iss. 10, 200402:18